Giao diện

- Giao diện song song 8bit/16bit

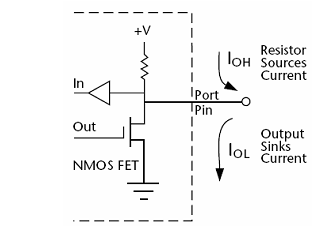

Các cổng song song là một dạng giao diện vào ra đơn giản và phổ biến nhất để kết nối thông tin với ngoại vi. Có nhiều loại cấu trúc giao diện vật lý điện tử từ dạng cổng vào ra đơn giản cực Collector TTL hở trong các ứng dụng cổng máy in đến các loại cấu trúc giao diện cổng tốc độ cao như các chuẩn bus IEEE-488 hay SCSI. Hầu hết các chip điều khiển nhúng có một vài cổng vào ra song song khả trình (có thể cấu hình). Các giao diện đó phù hợp với các cổng vào ra đơn giản như các khoá chuyển. Chúng cũng phù hợp trong các bài toán phục vụ giao diện kết nối điều khiển và giám sát theo các giao diện như kiểu rơle bán dẫn.

Hình 2.21: Cấu trúc nguyên lý điển hình của một cổng vào/ra logic

- Giao diện nối tiếp:

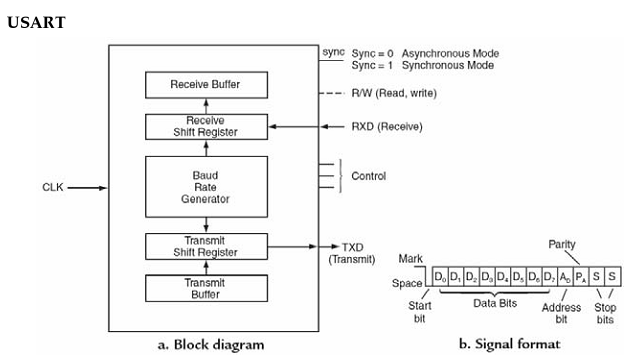

- USART:

Hình 2.22: Cấu trúc đơn giản hóa cuae USART

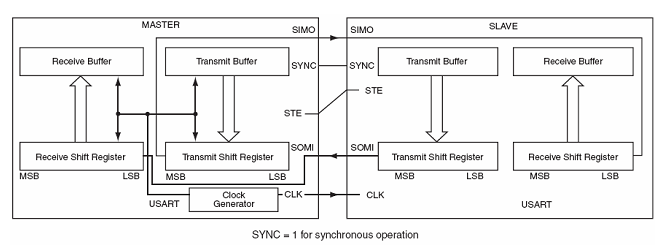

Hình 2.23: Mode hoạt động truyền thông đồng bộ

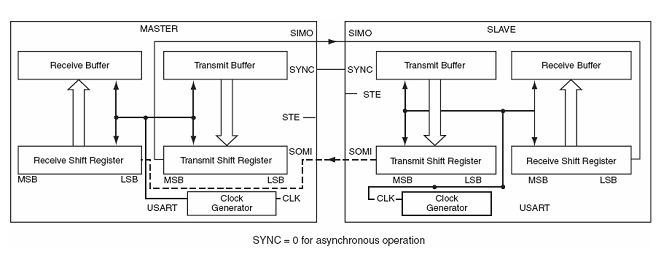

Hình 2.24: Mode hoạt động truyền thông dị bộ

- I2C (Inter-IC)

Giao thức ưu tiên truyền thông nối tiếp được phát triển bởi Philips Semiconductor và được gọi là bus I2C. Vì nguồn gốc nó được thiết kế là để điều khiển liên thông IC (Inter IC) nên nó được đặt tên là I2C. Tất cả các chíp có tích hợp và tương thích với I2C đều có thêm một giao diện tích hợp trên Chip để truyền thông trực tiếp với các thiết bị tương thích I2C khác. Việc truyền dữ liệu nối tiếp theo hai hướng 8 bit được thực thi theo 3 chế độ sau:

- Chuẩn (Standard)—100 Kbits/sec

- Nhanh (Fast)—400 Kbits/sec

- Tốc độ cao (High Speed)—3.4 Mbits/sec

Đường bus thực hiện truyền thông nối tiếp I2C gồm hai đường là đường truyền dữ liệu nối tiếp SDA và đường truyền nhịp xung đồng hồ nối tiếp SCL. Vì cơ chế hoạt động là đồng bộ nên nó cần có một nhịp xung tín hiệu đồng bộ. Các thiết bị hỗ trợ I2C đều có một địa chỉ định nghĩa trước, trong đó một số bit địa chỉ là thấp có thể cấu hình. Đơn vị hoặc thiết bị khởi tạo quá trình truyền thông là đơn vị Chủ và cũng là đơn vị tạo xung nhịp đồng bộ, điều khiển cho phép kết thúc quá trình truyền. Nếu đơn vị Chủ muốn truyền thông với đơn vị khác nó sẽ gửi kèm thông tin địa chỉ của đơn vị mà nó muốn truyền trong dữ liệu truyền. Đơn vị Tớ đều được gán và đánh địa chỉ thông qua đó đơn vị Chủ có thể thiết lập truyền thông và trao đổi dữ liệu. Bus dữ liệu được thiết kế để cho phép thực hiện nhiều đơn vị Chủ và Tớ ở trên cùng Bus.

Quá trình truyền thông I2C được bắt đầu bằng tín hiệu start tạo ra bởi đơn vị Chủ. Sau đó đơn vị Chủ sẽ truyền đi dữ liệu 7 bit chứa địa chỉ của đơn vị Tớ mà nó muốn truyền thông, theo thứ tự là các bit có trọng số lớn nhất MSB sẽ được truyền trước. Bit thứ tám tiếp theo sẽ chứa thông tin để xác định đơn vị Tớ sẽ thực hiện vai trò nhận (0) hay gửi (1) dữ liệu. Tiếp theo sẽ là một bit ACK xác nhận bởi đơn vị nhận đã nhận được 1 byte trước đó hay không. Đơn vị truyền (gửi) sẽ truyền đi 1 byte dữ liệu bắt đầu bởi MSB. Tại điểm cuối của byte truyền, đơn vị nhận sẽ tạo ra một bit xác nhận ACK mới. Khuôn mẫu 9 bit này (gồm 8 bit dữ liệu và 1 bit xác nhận) sẽ được lặp lại nếu cần truyền tiếp byte nữa. Khi đơn vị Chủ đã trao đổi xong dữ liệu cần nó sẽ quan sát bit xác nhận ACK cuối cùng rồi sau đó sẽ tạo ra một tín hiệu dừng STOP để kết thúc quá trình truyền thông.

I2C là một giao diện truyền thông đặc biệt thích hợp cho các ứng dụng truyền thông giữa các đơn vị trên cùng một bo mạch với khoảng cách ngắn và tốc độ thấp. Ví dụ như truyền thông giữa CPU với các khối chức năng trên cùng một bo mạch như EEPROM, cảm biến, đồng hồ tạo thời gian thực... Hầu hết các thiết bị hỗ trợ I2C hoạt động ở tốc độ 400Kbps, một số cho phép hoạt động ở tốc độ cao vài Mbps. I2C khá đơn giản để thực thi kết nối nhiều đơn vị vì nó hỗ trợ cơ chế xác định địa chỉ.

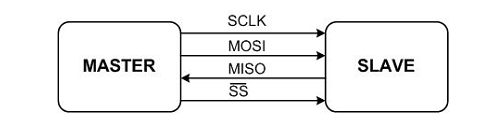

- SPI: SPI là một giao diện cổng nối tiếp đồng bộ ba dây cho phép kết nối truyền thông nhiều VĐK được phát triển bởi Motorola. Trong cấu hình mạng kết nối truyền thống này phải có một VĐK giữ vai trò là Chủ (Master) và các VĐK còn lại có thể hoặc là Chủ hoặc là Tớ. SPI có 4 tốc độ có thể lập trình, cực và pha nhịp đồng hồ khả trình và kết thúc ngắt truyền thông. Nhịp đồng hồ không nằm trong dòng dữ liệu và phải được cung cấp như một tín hiệu tách độc lập. Có ba thanh ghi SPSR, SPCR và SPDR cho phép thực hiện các chức năng điều khiển, trạng thái và lữu trữ. Có bốn chân cơ bản cần thiết để thực thi chuẩn giao diện truyền thông này:

- Dữ liệu ra MOSI (Master Output – Slave Input)

- Dữ liệu vào MISO (Master Input – Slave Output)

- Nhịp xung chuẩn SCLK (Serial Clock)

- Lựa chọn thành phần tớ SS (Slave Select)

Hình 2.25: Kết nối nguyên lý truyền thông SPI giữa mộy Master và Slave

Hình 2.25 chỉ ra nguyên lý kết nối giữa một đơn vị Chủ và một đơn vị Tớ trong truyền thông SPI. Trong đó tín hiệu SCLK sẽ được tạo ra bởi đơn vị Chủ và là tín hiệu vào của đơn vị Tớ. MOSI là đường truyền dữ liệu ra từ đơn vị Chủ tới đơn vị Tớ và MISO là đường truyền dữ liệu vào đơn vị Chủ đến từ đơn vị Tớ. Đơn vị Tớ được lựa chọn khi đơn vị Chủ kích hoạt tín hiệu SS.

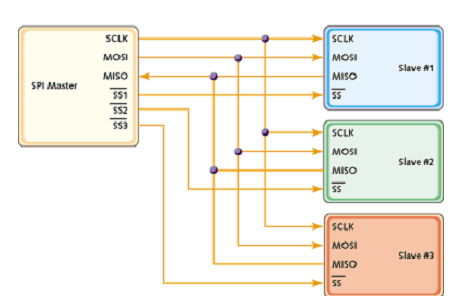

Hình 2.26: Sơ đồ kết nối truyền thống SPI của một đơn vị chủ với nhiều đơn vị tớ

Nếu hệ thống có nhiều đơn vị tớ đơn vị Chủ sẽ tạo phải ra các tín hiệu tách biệt để chọn đơn vị Tớ. Cơ chế đó được thực hiện nhờ sơ đồ kết nối nguyên lý mô tả như trong Hình 2.26. Đơn vị Chủ sẽ tạo ra tín hiệu chọn đơn vị Tớ nhờ các chân tín hiệu logic đa chức năng. Các tín hiệu này phải được điều khiển và đảm bảo ổn định về thời gian để tránh trường hợp tín hiệu bị thay đổi trong quá trình đang truyền dữ liệu. Một điều dễ nhận ra rằng SPI không hỗ trợ cơ chế xác nhận trong quá trình thực hiện truyền thông. Điều này phụ thuộc vào giao thức định nghĩa hoặc phải thực hiện bổ sung thêm một số các mở rộng phụ bên ngoài.

Khả năng truyền thông đồng thời hai chiều với tốc độ lên đến khoảng vài Mbit/s và nguyên lý khá đơn giản nên SPI hoàn toàn phù hợp để thực hiện truyền thông giữa các thiết bị yêu cầu truyền thông tốc độ chậm, đặc biệt hiệu quả trong các ứng dụng một đơn vị Chủ và một đơn vị Tớ. Tuy nhiên trong các ứng dụng với nhiều đơn vị Tớ việc thực thi lại khá phức tạp vì thiếu cơ chế xác định địa chỉ, và sự phức tạp sẽ tăng lên khi số đơn vị Tớ tăng.